Programmable logic and FPGAs

FPGAs are an excellent option for solutions that require high speeds and very high accuracy. FPGAs (Field-Programmable Gate Arrays) are programmable processors. They combine the speed, accuracy and security of hardware processors with the flexibility of software. FPGAs are a cost-effective option for highly demanding applications.

Programmable logic

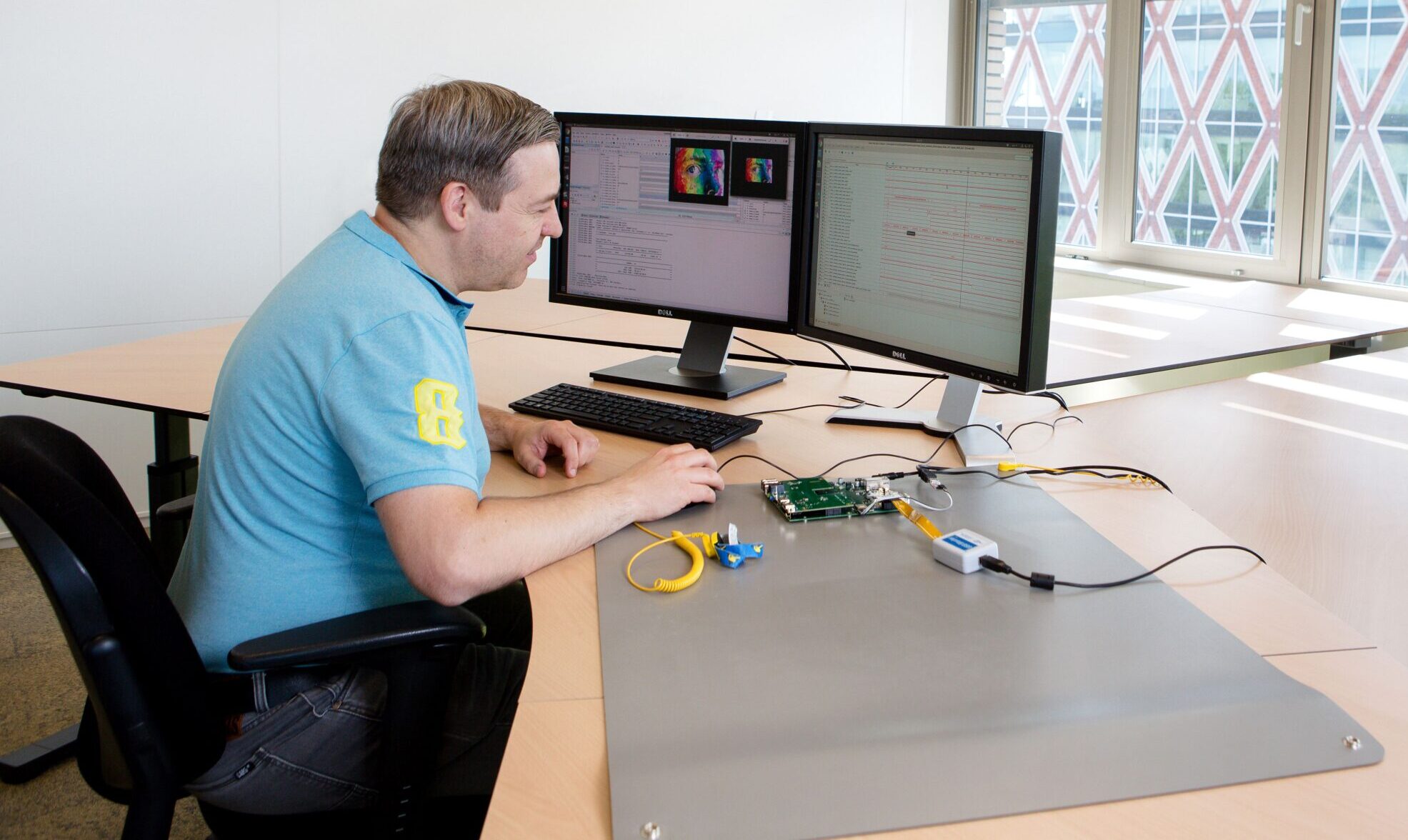

The greatest advantage of an FPGA is that it can be reprogrammed again and again. An FPGA-based system can therefore always be adapted to changing circumstances or new insights. FPGAs are programmed using programmable logic. This happens close to the hardware and requires specific expertise. TNL uses FPGAs to develop advanced applications, such as image processing systems, scientific metrology systems and security equipment for military use.

Structure and repeatability

We use structured methods and tools to develop FPGA applications. The processes are comparable to software development processes. The focus is on continuous integration, repeatability and reusability. Testing begins at an early stage in the process and is continually repeated. We record test processes in automated scripts, which also makes it possible to rapidly design tests for higher functional levels, and to use generic software (such as Python) for unit tests.

An automatic nightly build is run every night. This ensures automatic verification and validation of the logical components and embedded software produced. Errors in the logic are detected and solved at an early stage in the development process.

This structured, repeatable approach has great advantages for you as a client: even years after the original development, we can still repeat and/or adapt the design of your FPGAs.

FPGAs: supplier-independent

We are supplier-independent and work with all current brands of FPGA. If needed, we can build on your existing architecture. Our expertise includes Xilinx, Microchip, Intel, and radiation-hardened NanoXplore FPGA technology.

IP cores

We also like to use the strength of FPGAs and programmable logic for our own products, and we have so far developed many logical components (‘soft’ IP cores) of our own. Our engineers have even built a complete RISC-V softcore processor! TNL (Europe) is one of the founding members of the RISC-V Foundation (currently RISC-V International).

Our IP cores have been extensively tested and streamlined over time. We have a complete library of standard functionalities that are available immediately for use or reuse. This saves our clients time and money.

Our IP core library includes:

- Secure RISC-V (RV32IM) System-on-Chip (SoC) solutions;

- Fixed-/floating-point Xentium Digital Signal Processor (DSP) solutions;

- Image and video processing functionalities

Connectivity and interfaces (HDMI, USB, TCP/UDP, 1/10/100Gbps).

Our customer cases

Let’s talk about Programmable logic

And find out how we can help you